500억 개 트랜지스터 장착

45% 더 높은 성능 기대

양산까진 시간 소요 전망

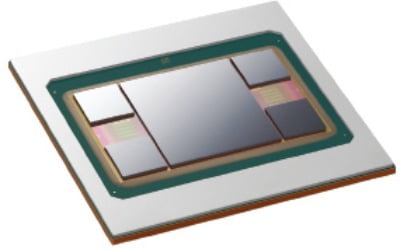

IBM은 6일 반도체 연구를 담당하는 IBM올버니연구소에서 세계 최초 2nm 나노시트 기반 반도체 테스트칩 개발에 성공했다고 발표했다. IBM 측은 “손톱만한 크기의 2나노 칩에 최대 500억 개의 트랜지스터를 장착할 수 있다”며 “더 작고, 더 빠르고, 더 안정적인 반도체를 구현하게 될 것”이라고 밝혔다.

'나노시트' 방식으로 공간 활용도 확보

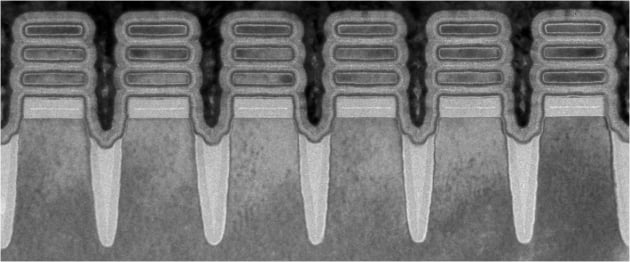

반도체는 칩에 집적된 트랜지스터 수가 많을수록 성능이 뛰어나다. 정보기술(IT) 업계가 더 미 세한 수준의 칩 설계에 사활을 거는 이유다. 현재도 삼성전자, TSMC 등 글로벌 반도체 업체들은 조금이라도 더 많은 소자를 배치하기 위해 트랜지스터 구조화 방식을 골몰하고 있다.이번 IBM의 2nm 테스트칩은 나노시트 기술을 바탕으로 개발된 첫 성공작이다. 그간 초미세 공정에서 주로 쓰여온 3D 구조 기반의 ‘핀펫(돌출형 게이트 배치)’ 방식이나 GAA(Gate All Around) 기반 ‘나노와이어(줄 모양의 게이트 배치)’ 방식과는 결이 다른 것으로 평가받는다. 나노시트는 특히 5nm 이하의 공정에서 힘을 발휘할 것이란 관측이 많다.

IBM은 2017년 삼성전자, 글로벌파운드리(GF)와 함께 5nm 칩 제조가 가능한 나노시트 생산 공정 개발에 성공한 바 있다. 2015년 200억 개의 트랜지스터를 집적할 수 있는 7나노 테스트 노드칩을 개발한 데 이어, 2년 만에 300억 개를 집적하는 기술을 개발했다.

배터리·자율주행 활용 기대…양산은 "장벽 존재"

같은 배치 방식을 기반으로 개발된 이번 테스트칩은 더욱 큰 폭의 성능 향상을 이뤄냈다. IBM 측은 “7나노 노드 칩보다 45% 더 높은 성능과 75% 더 낮은 에너지 사용량을 달성할 것”이라고 밝혔다. 휴대폰 배터리 수명을 4배 증가시키거나, 자율주행차가 물체를 감지하고 반응하는 시간을 크게 줄일 수 있다는 것이 회사 측 설명이다.다만 IT업계에선 실제 생산까지 이어지는 데 상당한 시간이 걸릴 것으로 내다보고 있다. 통상 테스트칩 개발과 제품 출하까지의 간극을 메우는 데는 오랜 시간이 걸린다. 가장 난관으로 꼽히는 공정 수율을 확보하고도 3년 이상의 시간이 소요되는 경우가 빈번하다.

현재 글로벌 선두주자로 꼽히는 삼성전자와 TSMC가 양산 가능한 최신 기술은 5nm 수준이다. 삼성전자는 지난해 1세대 5나노 제품 공급을 시작한 가운데, 올해 하반기 2세대와 3세대 제품 양산을 계획하고 있다. 지난 2018년 삼성전자가 “공정 성능의 검증을 끝냈다”던 3nm 기술 역시 아직은 양산이 어려운 상황이다. 2nm 기술이 제품화하기까지 걸릴 시간은 예측이 어렵다는 의견이 다수다.

이승우 유진투자증권 연구위원은 “테스트칩 개발과 공정 준비를 마쳤다는 것은 엄연히 다른 의미”라며 “삼성전자 등 글로벌 업체들이 내년도 3nm 양산을 목표하고 있다는 점을 고려하면, 2nm가 현실화하기까지 남은 장벽이 많을 것”이라고 전했다.

이시은 기자

![[단독] 美서 전력기기 품귀…LS·HD현대일렉 "5년치 일감 쌓였다"](https://img.hankyung.com/photo/202501/AA.39209575.3.jpg)

![[단독] "사복 경찰이 여자 집어던졌다"…서부지법 '아비규환'](https://img.hankyung.com/photo/202501/01.39234445.3.jpg)