1일 시장조사업체 카운터포인트리서치에 따르면 TSMC는 지난 2분기 세계 파운드리 시장에서 점유율(매출액 기준) 58%로 14%의 삼성전자와 격차를 벌렸다. 지난 1분기 조사에선 TSMC가 55%, 삼성전자가 17%였다.

2분기에는 TSMC와 삼성전자에 이어 대만 UMC(7%) 3위, 미국 글로벌파운드리(6%) 4위, 중국 SMIC(5%) 5위에 올랐다. 지난해 말과 비교하면 TSMC를 제외한 상위 4개 업체 시장점유율이 조금씩 떨어지면서 해당 점유율이 TSMC로 넘어간 형국이다.

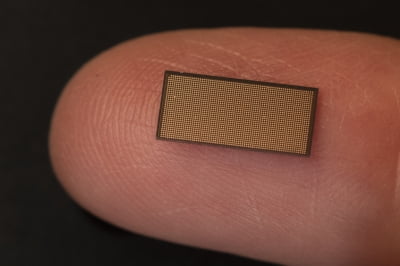

삼성전자와 TSMC는 파운드리 분야에서 초미세 공정 경쟁을 펼치고 있다. 현재 5나노(나노미터·1㎚는 10억분의 1m)급 칩을 양산하고 있는 곳은 이 두 곳밖에 없어 사실상 맞대결 구도가 형성됐다.

미세공정이 중요한 이유는 반도체는 더 얇게 설계할수록, 칩의 크기도 작아져 발열을 낮출 수 있기 때문. 발열을 낮추면 거꾸로 전력 효율을 높일 수 있다.

두 회사는 현재 내년 3나노 양산을 목표로 치열한 '속도전'을 진행 중이다. 3나노 양산에 먼저 성공하는 쪽이 애플, 구글 등 대형 고객사를 선점할 가능성이 높아서다.

반도체 업계에선 3나노 양산을 시작한다고 해도 수율 안정화까지는 3~4년이 걸릴 것으로 본다. 삼성전자가 이를 얼마나 단축시켜 TSMC를 따라잡느냐가 3나노 공정 경쟁의 관건이다.

때문에 삼성전자는 그동안 사용하지 않던 게이트 올 어라운드(GAA) 기술을 채택했다. 기존 핀펫(FinFET) 구조보다 기술적으로 고난도지만 전력효율이 더 나은 것으로 알려졌다. 삼성전자는 GAA 기술을 채택한 3나노 공정과 관련해 내년 양산을 목표로 차질없이 개발 중이라고 밝혔다.

반대로 TSMC는 기존에 쓰던 핀펫 기술을 적용해 예정대로 내년 7월이면 3나노 칩 양산에 성공할 것이란 게 업계 관측이다. TSMC는 최근 대만 타이난에 있는 '팹18' 공장에 3나노 공정 장비를 설치한 것으로 알려졌다.

노정동 한경닷컴 기자 dong2@hankyung.com