TSMC 잡을 3나노…삼성이 한 발 빨랐다

-

기사 스크랩

-

공유

-

댓글

-

클린뷰

-

프린트

삼성 '3나노 반도체' 첫 양산

TSMC에 '기술 초격차'로 승부

미세공정 반도체 시장서 주도권

소비전력 줄고 처리 속도 올라가

관건은 수율…안정화엔 3~4년

TSMC에 '기술 초격차'로 승부

미세공정 반도체 시장서 주도권

소비전력 줄고 처리 속도 올라가

관건은 수율…안정화엔 3~4년

결과는 반대였다. 삼성전자는 30일 GAA(gate-all-around) 기술을 적용한 3㎚ 반도체 양산에 들어갔다고 발표했다. TSMC보다 한발 빠른 행보다. 기술 리더십을 증명한 삼성전자가 고객사 확보에 유리한 고지를 점했다는 평가가 나온다.

GAA 기술로 성능 확보

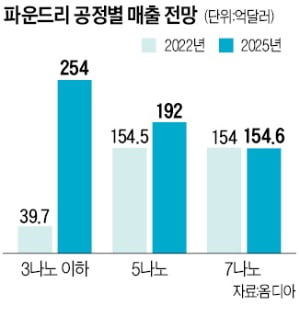

반도체 생산에서 미세공정이 중요한 것은 반도체 회로 폭이 좁아질수록 소자 동작이 빨라지기 때문이다. 부가 효과도 있다. 소비전력이 줄어들고 정보 처리 속도는 올라간다. 회로를 얇게 그릴수록 웨이퍼 한 장에서 더 많은 반도체를 제조할 수 있어 생산성도 올라간다.

삼성전자는 누설 전류에 따른 반도체 오작동과 성능 저하를 줄이기 위해 기존 5㎚ 반도체에선 핀펫 공정을 활용했다. 삼성전자가 3㎚ 공정에 활용한 GAA 기술은 핀펫 기술에 비해 전류를 제어할 접점을 넓혔다는 점에서 차별화된다. 3㎚ GAA 1세대 공정은 기존 5㎚ 핀펫 공정과 비교해 전력은 45% 절감되고 성능은 23% 향상됐으며 면적은 16% 축소됐다. 내년에 나오는 3㎚ GAA 2세대 공정은 전력은 50% 절감되고 성능은 30% 향상되며 면적은 35% 축소될 것으로 기대된다.

이번 3㎚ 공정은 첨단 파운드리 극자외선(EUV) 장비를 쓰는 삼성전자 화성캠퍼스 S3 라인에 적용된다. 삼성전자는 고성능 컴퓨팅(HPC)용 시스템 반도체 양산에 3㎚ 공정을 우선 활용하고 모바일 반도체 등으로 확대한다는 방침이다.

최시영 삼성전자 파운드리사업부장(사장)은 “차별화된 기술을 적극 개발하고, 공정 성숙도를 빠르게 높이는 시스템을 구축해 나가겠다”고 밝혔다.

안정적인 수율 확보가 관건

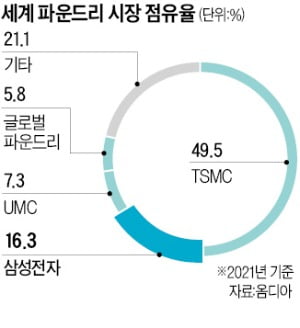

삼성전자는 3㎚ 반도체 양산을 계기로 세계 1위 파운드리(반도체 수탁생산) 기업 TSMC 추격에 속도를 낼 계획이다. 파운드리 전체 시장에선 TSMC의 점유율이 삼성의 세 배 이상이지만, 10㎚ 이하 미세공정 반도체 시장에선 6 대 4로 양강 구도를 형성하고 있다. 두 회사 외에는 이렇다 할 경쟁자가 없다.

변수는 수율이다. 3㎚ 공정에서 안정적인 수율을 확보해야 수익성을 끌어올릴 수 있기 때문이다. 유회준 KAIST 전자공학과 교수는 “수율이 안정화되는 데까지 보통 3~4년 걸린다”며 “삼성전자가 존재감을 키우려면 이 기간을 최대한 단축해야 한다”고 말했다.

박신영/정지은 기자 nyusos@hankyung.com

![K팝 업계에도 '친환경' 바람…폐기물 되는 앨범은 '골칫거리' [연계소문]](https://img.hankyung.com/photo/202206/99.27464274.3.jpg)