반도체 패키징 전력 소모 95% 줄이는 기술 나왔다

-

기사 스크랩

-

공유

-

댓글

-

클린뷰

-

프린트

한국전자통신연구원(ETRI) 개발

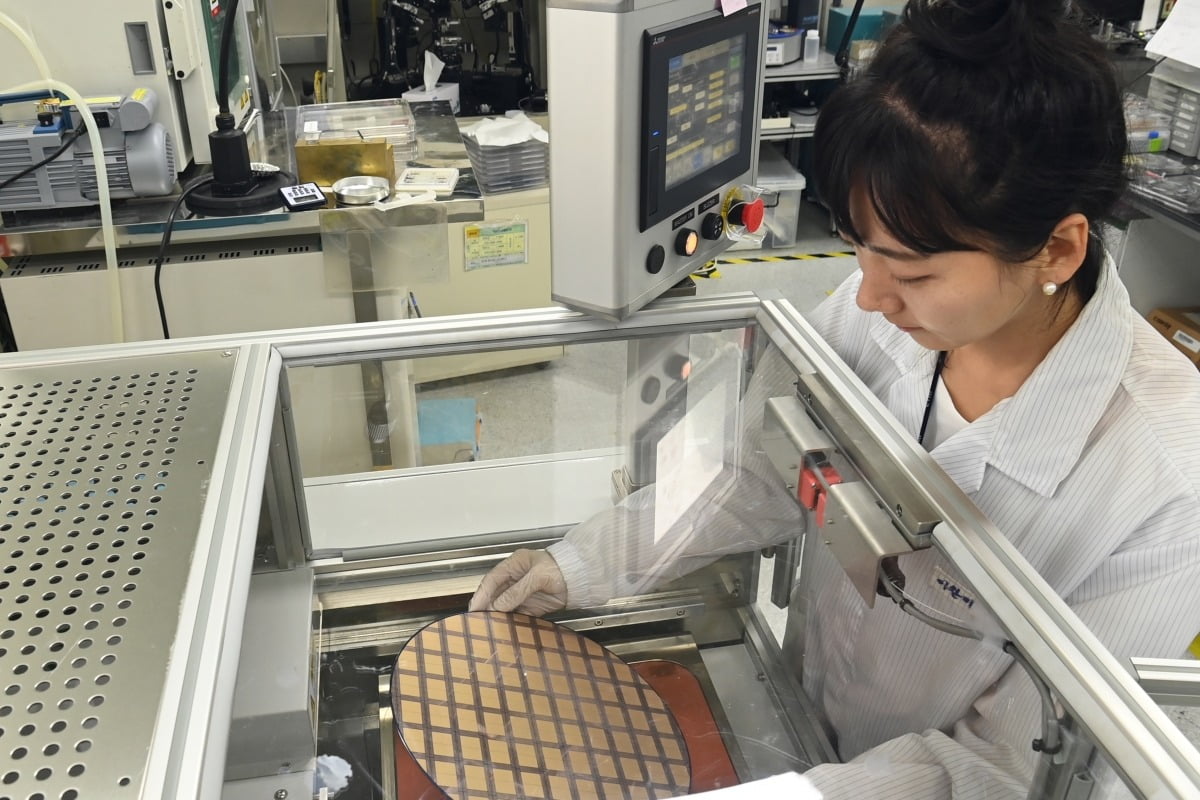

한국전자통신연구원(ETRI)은 창의원천연구본부 연구진이 자체 보유한 나노 소재 기술을 활용해 일본이 보유한 패키징 기술 대비 95% 전력 절감이 가능한 반도체 칩렛 패키징 기술을 개발했다고 28일 밝혔다.

칩렛은 고성능 칩을 기능별로 분리해 작게 만들고 수율을 증가시켜 전체 비용을 낮추는 기술이다. 시장조사기관 욥디벨롭먼트에 따르면 2027년 칩렛 패키징 시장 규모는 240억달러(약 30조원)에 달할 것으로 전망된다.

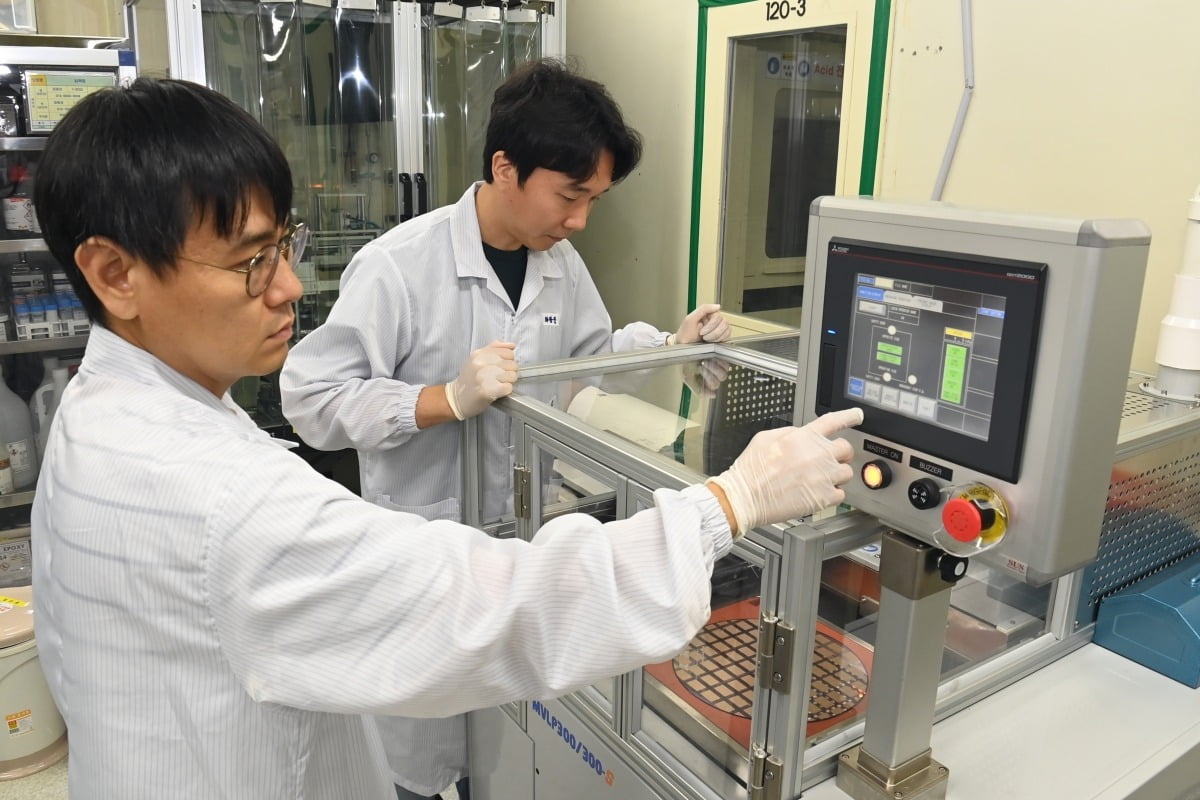

반도체는 웨이퍼 제조→산화→포토→식각→증착→배선→EDS→패키징 과정을 통해 생산한다. 포토, 식각 등과 마찬가지로 패키징 공정에서도 일본 소재를 주로 써왔다. 일본 소재 기반 패키징 공정은 플럭스 도포, 리플로우(레이저 접합), 세척, 건조, 플라즈마 처리, 언더필(응력 완화제) 도포, 언더필 경화 등 9단계 공정을 거쳐야 했다. 전력 소모가 높고 청정실 유지 비용이 비싼 데다 유해물질 배출이 적지 않았다.

또 칩렛 집적에 필요한 칩간 연결통로인 접합부를 세척하기 어렵고, 상온에서 접합이 어렵다는 단점이 있었다. TSMC, 삼성전자, 인텔 등은 이런 복잡한 후공정 과정을 간소화하기 위한 기술을 개발하고 있다.

ETRI 관계자는 "기존엔 웨이퍼에서 분리한 칩을 보드에 붙여 한 개씩 잘라 쓰는 방식이었다면, 우리 기술을 쓰면 칩렛을 웨이퍼 기판에 타일 붙이듯 찍어 붙이는 게 가능하다"고 말했다.

이어 "본 기술은 공정이 간단해 전체 생산라인을 기존 20m에서 20% 수준인 4m로 줄일 수 있다"며 "질소 가스도 필요없어 유해물질이 발생하지 않는다"고 덧붙였다.

현재 글로벌 파운드리 기업이 ETRI가 개발한 후공정 기술 신뢰성을 평가하고 있는 것으로 알려졌다. ETRI는 이 기술과 관련해 23건의 특허를 국내외에 출원 또는 등록했다. 관련 논문은 최근 글로벌 반도체 패키징 학회인 2023 IEEE ECTC에서 발표됐다.

이해성 기자 ihs@hankyung.com

![K팝 업계에도 '친환경' 바람…폐기물 되는 앨범은 '골칫거리' [연계소문]](https://img.hankyung.com/photo/202206/99.27464274.3.jpg)