삼성전자 "2027년 1.4나노 양산…원스톱 AI 솔루션 강화"

-

기사 스크랩

-

공유

-

댓글

-

클린뷰

-

프린트

삼성전자, 삼성 파운드리 포럼 2024 개최

로드맵 발표…1.4나노 양산 2027년 재확인

"AI칩 개발·생산·조립 원스톱 서비스 강화"

2나노 공정에 후면전력공급·광학 소자 기술 도입

로드맵 발표…1.4나노 양산 2027년 재확인

"AI칩 개발·생산·조립 원스톱 서비스 강화"

2나노 공정에 후면전력공급·광학 소자 기술 도입

삼성전자는 12일(현지시간) 미국 실리콘밸리에서 '삼성 파운드리 포럼 2024'를 개최하고 AI 시대를 주도할 반도체 파운드리 부문의 기술 전략을 공개했다. 이번 행사는 'AI 혁신 강화(Empowering the AI Revolution)'를 주제로 삼성전자의 최선단 파운드리 기술과 차별화 전략을 제시했다.

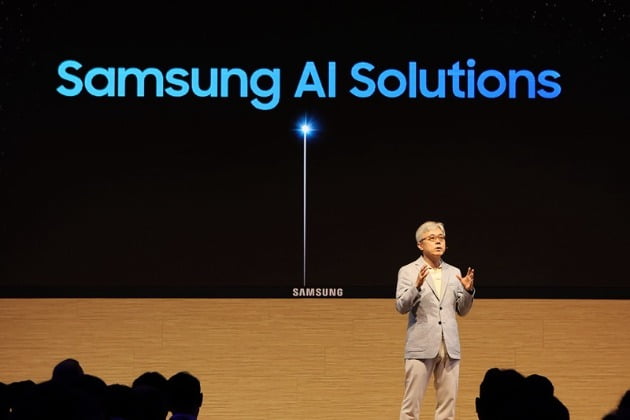

최시영 삼성전자 파운드리 사업부 사장은 기조연설에서 "삼성전자는 AI 반도체에 최적화된 GAA(게이트올어라운드) 공정 기술과 적은 전력 소비로도 고속 데이터 처리가 가능한 광학 소자 기술 등을 통해 AI 시대에 고객들이 필요로 하는 원스톱 AI 솔루션을 제공할 것"이라고 말했다.

삼성전자는 현재 파운드리의 시스템 반도체와 메모리의 고대역폭메모리(HBM), 이를 패키징하는 통합 'AI 솔루션'을 통해 AI 칩 제품을 출시하고 있다. 삼성의 AI 솔루션을 활용하는 팹리스 고객은 각 부문별 업체를 별도로 거치는 기존 공정보다 칩 개발에서부터 생산까지 걸리는 시간을 약 20% 단축할 수 있다고 설명했다.

2027년에는 새로운 파운드리 기술을 도입하기로 했다. 우선 2027년까지 2나노 공정에 후면전력공급(BSPDN) 기술을 도입(SF2Z)한다. 내년부터 양산 계획인 2나노 공정 적용 반도체에 BSPDN 기술을 탑재한다는 것이다. BSPDN은 전력선을 웨이퍼 후면에 배치해 전력과 신호 라인의 병목 현상을 개선하는 기술로 아직 상용화 사례가 없다. 또한 SF2Z는 기존 2나노 공정 대비 PPA(소비전력·성능·면적) 개선 효과뿐 아니라, 전류의 흐름을 불안정하게 만드는 전압강하 현상을 줄여 고성능 컴퓨팅 설계 성능을 향상시킬 수 있다.

그동안 웨이퍼 앞면에 회로를 그리던 반도체 전력선을 후면에도 그리게 되면 초미세화 공정을 구현할 수 있을 것으로 기대된다. 앞서 대만 TSMC는 2026년 말 2나노 이하 1.6공정에 후면전력공급 기술을 도입하겠다고 밝힌 바 있다.

다만 업계의 기대를 모았던 1.4나노 공정 양산 시기 단축 발표는 나오지 않았다. 앞서 지난 4월 TSMC가 2026년부터 1.6나노 공정 양산 계획을 발표하며 1나노대 양산 일정을 앞당긴 만큼 삼성전자의 1나노대 공정 로드맵에 시선이 모인 바 있다.

삼성전자는 이날 2027년 1.4나노 공정 양산 계획을 재확인했다. 삼성전자는 "(1.4나노 공정 관련) 목표한 성능과 수율을 확보하고 있다"고만 밝혔다.

최 사장은 "AI를 중심으로 모든 기술이 혁명적으로 변하는 시점에서 가장 중요한 건 AI 구현을 가능하게 하는 고성능·저전력 반도체"라며 고객 수요에 대응하겠다고 밝혔다.

오정민 한경닷컴 기자 blooming@hankyung.com

![K팝 업계에도 '친환경' 바람…폐기물 되는 앨범은 '골칫거리' [연계소문]](https://img.hankyung.com/photo/202206/99.27464274.3.jpg)