반도체칩 더 촘촘히 쌓게…패키징 장비 국산화

-

기사 스크랩

-

공유

-

댓글

-

클린뷰

-

프린트

코스텍시스템·네패스 손잡고

웨이퍼 휨 막는 기술 개발

일본산보다 30% 싸게 공급

웨이퍼 휨 막는 기술 개발

일본산보다 30% 싸게 공급

지난해 기준 국내 후공정업체 총매출은 20억달러로 세계 시장(341억달러)의 5.8%에 그쳤다. 이들을 육성하기 위해 정부와 업계가 공동 연구개발(R&D)에 나선 이유다.

수입에 의존하던 반도체 장비 국산화

이 장비는 네패스가 현재 사용하는 기술인 팬아웃(fan-out) 반도체칩 패키지 공정에서 웨이퍼의 휨 현상을 보완하기 위해 지지대(캐리어 웨이퍼)를 임시로 붙였다가 떼는 것이다.

반도체는 집적도를 높이기 위해 3차원(3D)으로 칩을 쌓는다. 그러려면 디바이스 웨이퍼(혹은 패널) 뒷면을 갈고 이를 관통하는 수천 개의 미세 구멍(TSV)을 뚫어야 하고, 이 과정에서 웨이퍼의 휨을 막아야 하는데 이것이 핵심 기술이다. 접착 필름을 붙일 때 빈 공간이 생기지 않도록 압력을 조절하는 기술, 300㎛ 웨이퍼에 부착한 필름접착제 및 보호필름을 떼는 기술이 모두 코스텍의 자체 특허 기술로 구현됐다.

코스텍은 임시 접착제로 필름을 사용해 네패스의 최종 양산테스트를 통과했다. 그동안 시장을 장악한 독일 오스트리아 일본산 제품 가격(70억~140억원)보다 30% 저렴해 시장 경쟁력을 갖출 것으로 예상된다.

산업통상자원부와 한국산업기술평가관리원이 2017년부터 3년간 지원(수요자 연계형 소재부품개발사업)해 준 덕분이다. 김용섭 코스텍시스템 전무는 “일본의 수출규제와 정부의 지원정책, 업계의 국산화 의지가 한데 모인 결과”라고 말했다.

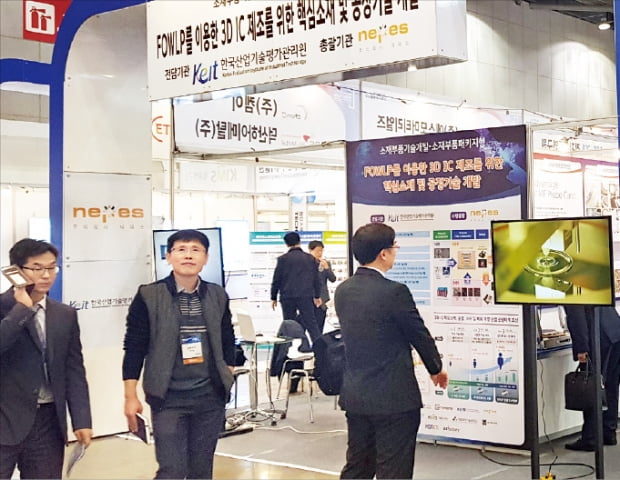

16개 기업·기관 공동 R&D에 150억원 투입

‘팬아웃 웨이퍼 레벨 패키지(FOWLP)를 이용한 3D 집적회로(IC) 제조를 위한 핵심소재 및 공정기술개발’ 사업은 네패스(총괄 주관기업)를 포함해 16개 기업과 대학·기관이 함께하고 있다. 5년간 총 사업비는 154억여원에 달한다.

웨이퍼 레벨 패키지(WLP)는 칩을 작고 얇게 생산할 수 있는 초미세 패키징 기술로 스마트폰 자동차 통신기기에 들어가는 첨단 반도체에 적용된다. 팬아웃 패키지는 반도체칩 공정이 미세화되면서 좁아진 칩 면적에서 입출력 단자 배선을 바깥으로 빼내는 기술이다.

김종헌 네패스 전무는 “국내에서 정부가 지원하는 단일 R&D사업으로는 보기 힘든 규모”라며 “네패스가 이미 글로벌 수준의 생산을 하고 있지만 여러 소재, 부품, 테스트 장비 중소·중견기업들과 협력하며 국내 시스템 반도체 산업의 경쟁력을 한층 높이는 계기가 될 것”이라고 말했다.

공동 개발에는 켐이, 마이크로프랜드, 덕산하이메탈, 에스모스소재기술연구소, 서울테크노파크, 서울과학기술대, 한국전자기계융합기술원 등이 참여하고 있다.

오송·평택=문혜정 기자 selenmoon@hankyung.com

![[문혜정의 핫템, 잇템] 세탁기 3시간 동안 분해·세척…숨은 물때·곰팡이 '싹~'](https://img.hankyung.com/photo/201912/AA.21124093.3.jpg)

![K팝 업계에도 '친환경' 바람…폐기물 되는 앨범은 '골칫거리' [연계소문]](https://img.hankyung.com/photo/202206/99.27464274.3.jpg)