TSMC 잡을 삼성 최첨단 기술…'3nm GAA' 공정의 숨은 공신 [실리콘밸리 나우]

-

기사 스크랩

-

공유

-

댓글

-

클린뷰

-

프린트

'3nm GAA 공정'의 숨은 공신

美 반도체 EDA 전문업체 시놉시스

최근 "3nm GAA 공정 설계 완료" 발표

GAA는 삼성이 개발 중인 최첨단 기술

TSMC 잡을 비밀무기로 꼽혀

초전력, 고성능 칩을 효율적으로 제작

삼성전자 파운드리 설계 협업 강화

시놉시스 연 매출 9.5% 증가 전망

美 반도체 EDA 전문업체 시놉시스

최근 "3nm GAA 공정 설계 완료" 발표

GAA는 삼성이 개발 중인 최첨단 기술

TSMC 잡을 비밀무기로 꼽혀

초전력, 고성능 칩을 효율적으로 제작

삼성전자 파운드리 설계 협업 강화

시놉시스 연 매출 9.5% 증가 전망

시놉시스는 보도자료에 복잡한 통합칩셋(SoC, 다양한 기능의 소자를 배치해 원칩으로 만든 반도체)의 '테이프아웃'을 한 번에 성공했다고 적었다. 테이프아웃은 칩의 설계를 최종적으로 마쳤다는 뜻이다. 향후 삼성전자는 이를 검증한 뒤 3nm 파운드리 공정 시험생산을 시작할 것으로 전망된다. 물론 TSMC도 현재 3nm 공정을 개발 중이다. 닛케이아시안리뷰는 최근 "TSMC가 인텔과 애플에 3nm 공정용 시제품을 보냈다"고 보도했다. 그럼에도 불구하고 시놉시스의 발표가 의미 있는 건 삼성전자의 3nm(나노미터, 10억분의 1m) 공정에 'GAA(Gate All Around)' 기술이 적용된다는 점을 다시 한 번 확인했다는 것이다. TSMC는 3nm 공정에 GAA 기술을 적용하지 않기로 했다.

TSMC 잡을 삼성전자의 무기 'GAA'

GAA는 삼성전자 파운드리(반도체 수탁생산)사업의 차세대 핵심 기술이다. 세계 1위 파운드리업체 TSMC를 추격할 수 있는 비장의 무기로 꼽힌다. 파운드리사업의 성패는 고성능·저전력·초소형 반도체를 얼마나 효율적으로 제작할 수 있는 지에 달려 있다. 더 많은 고객의 주문을 받아 반도체를 생산하고(파운드리), 성능이 뛰어난 AI칩, 자율주행칩 등을 만들어 TSMC를 뒤집기 위해선 압도적인 기술력이 필수다. 삼성전자의 GAA는 그런 기술로 꼽힌다.반도체에서 전류를 흐르게 하는 '스위치' 역할을 하는 트랜지스터와 관련이 있는 기술이다. 트랜지스터에서 가장 중요한 부분이 '게이트'다. 게이트에 전압을 가하면 게이트와 맞닿아 있는 '채널'이 전기의 길을 열고 반대의 경우 전류를 차단한다. 반도체의 성능은 게이트와 채널에서 누설전류를 얼마나 줄이고 효율적으로 관리하느냐에 갈린다고 한다. 트랜지스터에서 전류를 컨트롤하는 게이트와 채널이 닿는 면적이 클수록 전력 효율성이 높아지는 것이다.

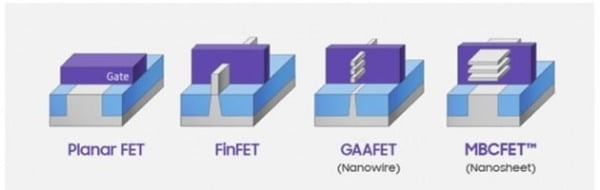

과거에 많이 썼던 '평판' 트랜지스터는 게이트와 채널이 하나의 면으로 맞닿아 있는 '2D' 구조다. 반도체 공정이 미세화될수록 트랜지스터 크기가 줄고, 게이트와 채널이 맞닿는 면적도 작아져 제 역할을 못하는 문제가 늘었다.

더 미세한 3nm 공정에선 핀펫구조의 한계가 발생한다는 것이다. 그래서 삼성전자가 개발한 미래 기술이 GAA다. GAA는 3면에서 채널과 게이트가 접했던 핀펫구조와 달리 게이트가 '채널 4면'을 둘러싸게 한 것이다. 좀 더 세밀하게 전류를 조정할 수 있게해 높은 전력효율을 얻을 수 있도록 한 것이다. 삼성전자는 3nm 공정에서부터 GAA 기술을 활용할 계획이다.

시놉시스, 삼성전자와 3nm 공정 설계 협업

그렇다면 왜 삼성전자가 아닌 시놉시스가 GAA 기술 관련 발표를 한 것일까. 반도체 산업의 사슬과 연관이 있다. 팹리스(반도체 설계전문 업체), 파운드리는 각각 또는 공동으로 반도체를 설계하고 개발한다. 이 때 활용하는 게 EDA다. 쉽게 말해 반도체를 설계할 때 필수적인 소프트웨어다. 설계는 물론 검증에도 활용된다. EDA 툴이 훌륭할수록 팹리스의 설계 능력과 팹리스의 설계대로 칩을 만드는 파운드리의 경쟁력이 올라갈 수 밖에 없는 구조인 것이다. 시놉시스는 EDA 매출이 전체 매출의 60% 수준이다.(2020년회계연도엔 57%)

반도체 개발에 없어선 안 될 중요한 기술로 인식되면서 시놉시스 인력에 대한 이직 제의도 활발한 것으로 알려졌다. 특히 미국의 반도체 수출 규제로 시놉시스의 설계 툴을 활용하지 못하게 된 중국 반도체 기업들이 최근 시놉시스 인력들에게 적극적으로 '러브콜'을 보내고 있는 것으로 알려졌다.

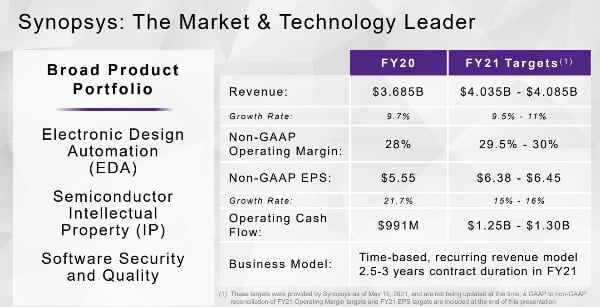

시놉시스 매출, 전년 대비 9.5% 증가 전망

시놉시스의 실적은 어느 수준일가. 회사가 지난 5월 콘퍼런스콜(전화 실적설명회)을 통해 공개한 2021회계연도 상반기(2020년 11월~2021년 4월) 영업이익은 총 3억4258만달러(약 3920억원)다. 전년 동기(2억1341만달러)보다 60.5% 늘었다.회사가 제시한 2021회계연도(2020년 11월~2021년 10월) 전체 매출 전망치는 40억3500만~40억8500만달러(4조6342억원~4조6916억원)다. 2020회계연도 매출 36억8528만달러보다 최소 9.5% 증가할 것으로 예상된 것이다. 주당 순이익도 2020년 5.55달러에서 2021년 6.38~6.45달러로 증가할 전망이다..

시놉시스는 나스닥에 상장돼있다. 지난 9일 기준 종가는 280.75달러, 시가총액은 428억3500만달러다. 지난 2월 292.09달러로 최고점을 찍고 3월 218.49달러로 떨어진 이후 28.5% 반등했다. 가장 최근 투자의견을 제시한 증권사는 미국 로젠블라트다. 지난 6월 목표주가 302달러를 제시했다. 가장 높은 목표주가는 지난 2월 RBC캐피탈과 UBS가 예상한 330달러다. 리스크 요인으론 강력한 EDA 시장의 경쟁자 '케이던스(Cadence)'의 존재, 미국의 중국 반도체 규제에 따라 시장 확장세가 주춤해진 점이 꼽힌다.

실리콘밸리=황정수 특파원 hjs@hankyung.com

![[ESG 브랜드 랭킹]LG그룹, 지배구조 톱 10 중 절반 차지](https://img.hankyung.com/photo/202106/01.26813396.3.jpg)

![코로나에 직원들 없는데…'방범 로봇'이 지키는 빅테크기업 [실리콘밸리나우]](https://img.hankyung.com/photo/202107/01.26901642.3.jpg)

![[포토] 삼성전자 “빔 프로젝터 ‘더 프리미어’ 워커힐 호텔서 체험”](https://img.hankyung.com/photo/202107/AA.26903178.3.jpg)