승부수 띄운 삼성전자…"TSMC의 미세공정, 위로 쌓아서 넘겠다"

입력

수정

EUV 시스템반도체 3차원 적층 패키징 기술 개발

업계 최초로 7나노 공정에 적용

시스템반도체 '초격차' 전략 가속화

삼성전자는 13일 3차원 적층 패키지 기술인 ‘엑스큐브(X-Cube)’를 활용해 만든 테스트칩 생산에 성공했다고 발표했다. EUV 전공정뿐 아니라 후공정에서도 첨단 기술 경쟁력을 확보하게 됐다는 것이 회사 측 설명이다.

엑스큐브는 삼성전자의 파운드리 고객사를 겨냥해 내놓은 기술이다. 고객사들이 엑스큐브 설계방법론과 설계도구 등을 활용해 EUV 기술 기반 칩 개발에 바로 들어갈 수 있게 했다. 이미 업계에서 검증이 끝난 삼성전자의 양산 인프라를 이용할 수 있기 때문에 칩 개발 기간을 줄일 수 있다는 것이 회사 측 설명이다.

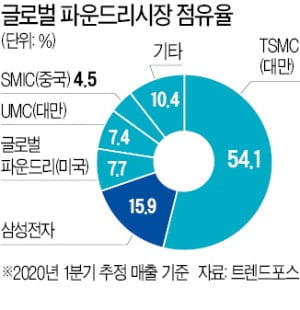

업계에서도 삼성전자 엑스큐브 기술의 가치를 높게 평가하고 있다. 파운드리 업계 1위인 TSMC와 경쟁할 수 있는 무기를 얻었다는 것이 전문가들의 중론이다. 미세공정 기술 전쟁에서 TSMC는 삼성전자에 한 발 앞서있다. 이미 올해 상반기부터 5㎚(나노미터, 1㎚=10억분의 1m) 공정을 활용해 양산품을 찍어내고 있다. 업계 관계자는 “7나노 공정에 엑스큐브 기술을 적용하면 5㎚ 공정에 못지않은 품질의 제품을 만들 수 있다”며 “TSMC와의 기술력 격차가 거의 사라졌다고 볼 수 있다”고 설명했다. 시장조사업체 트렌드포스에 따르면 올해 1분기 기준 TSMC의 시장점유율은 54.1%다. 삼성전자는 업계 2위지만 점유율이 15.9%에 불과하다. 삼성전자와 경쟁 관계인 인텔, 퀄컴 등이 기술 유출을 우려해 TSMC에만 칩 생산을 맡기고 있다보니 점유율 차이가 줄지 않고 있다. 기술력도 점유율 차이를 설명하는 요인 중 하나다. 굳이 대안을 찾지 않을 만큼 TSMC의 기술 높다는 설명이다.

한편 삼성전자는 오는 16일부터 18일까지 온라인으로 진행되는 고성능 반도체 연례 학술 행사인 ‘핫 칩스 2020’'에서 엑스큐브의 기술 성과를 공개할 계획이다.

송형석 기자 click@hankyung.com